반도체/FPGA - Verilog

[FPGA] Clock에 필요한 모듈 2) FND 4digit switcher Verilog Code

쑨야미

2021. 4. 1. 19:33

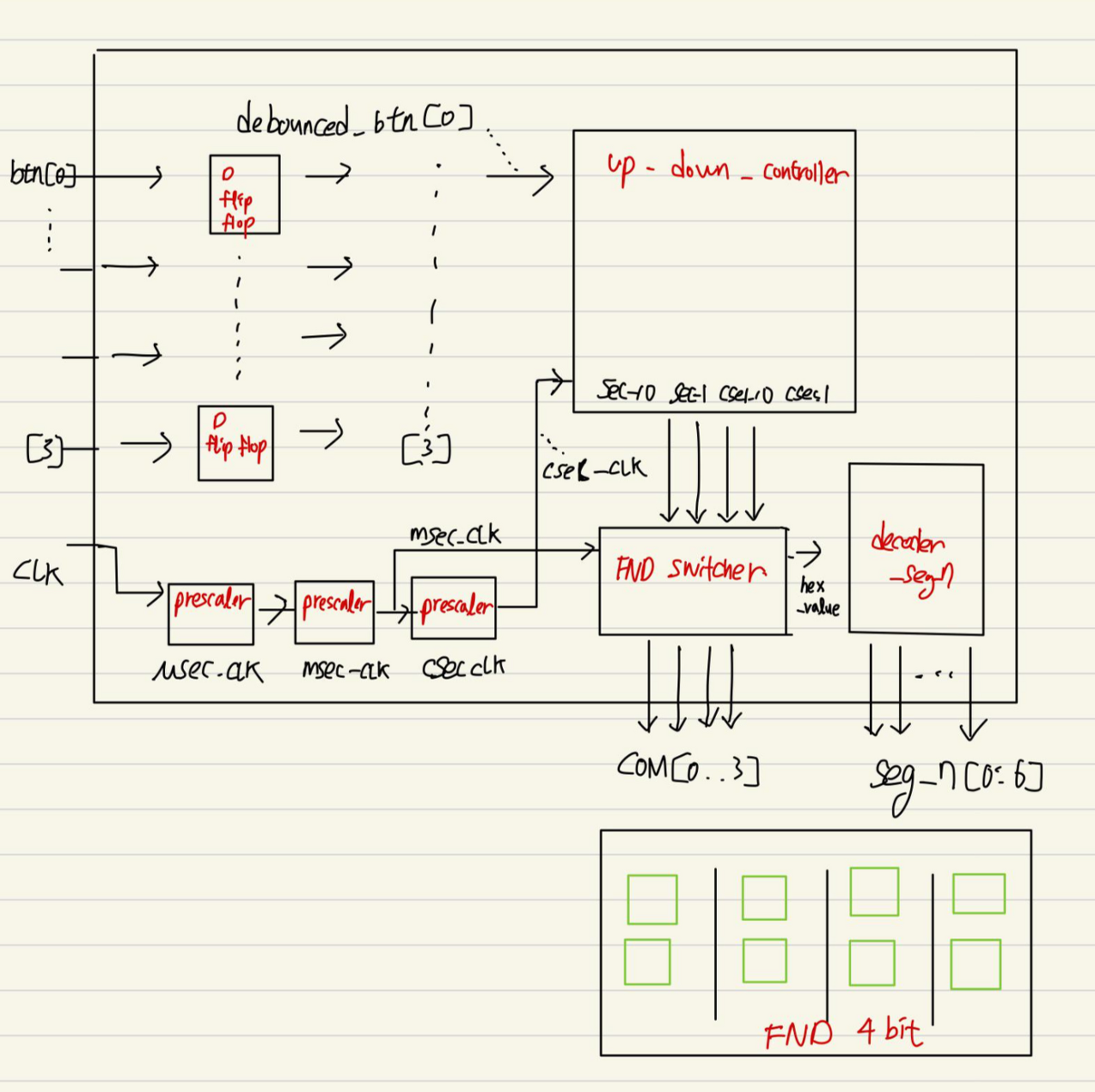

prescaler를 통해서 나눠진 단위 clock들에 맞춰 Up/Down Conuter모듈을 지나 생성된 초분시에 대한 Data는

4bit의 COM[0:3] 출력으로 나온다. 이 COM 출력은 4자리의 FND출력의 자리를 나타내는 Data이다.

따라서 이 자리수 데이터 값을 나타내는 FND Switcher 코드는 다음과 같다.

module FND4digit_switcher(

input [3:0] value_1,

input [3:0] value_10,

input [3:0] value_100,

input [3:0] value_1000,

input clk_msec,

output reg [3:0] com,

output reg [3:0] hex_value

);

always @(negedge clk_msec) begin

case(com)

4'b0111: begin

com = 4'b1110;

hex_value = value_1;

end

4'b1110: begin

com = 4'b1101;

hex_value = value_10;

end

4'b1101: begin

com = 4'b1011;

hex_value = value_100;

end

4'b1011: begin

com = 4'b0111;

hex_value = value_1000;

end

default: begin

com = 4'b0111;

hex_value = value_1000;

end

endcase

end

endmodule주의할점은 2진수로 나타낸 Com 값은 FND가 애노드 타입인지 캐소드 타입인지에 따라서 다르다.

서로 보수이니 맞춰서 설정하면된다.

1. Prescaler

2021.04.01 - [반도체/FPGA - Verilog] - [FPGA] Clock에 필요한 모듈 1) Prescaler Verilog Code

3. Decoder 7_seg

2021.04.01 - [분류 전체보기] - [FPGA] Clock에 필요한 모듈 3) Decoder for 7 Segments Verilog Code

4. UP/DOWN Counter

2021.04.01 - [분류 전체보기] - [FPGA] Clock에 필요한 모듈 4) Up/Down Counter Verilog Code