반도체/FPGA - Verilog

[FPGA] Clock에 필요한 모듈 4) Up/Down Counter Verilog Code

쑨야미

2021. 4. 1. 19:46

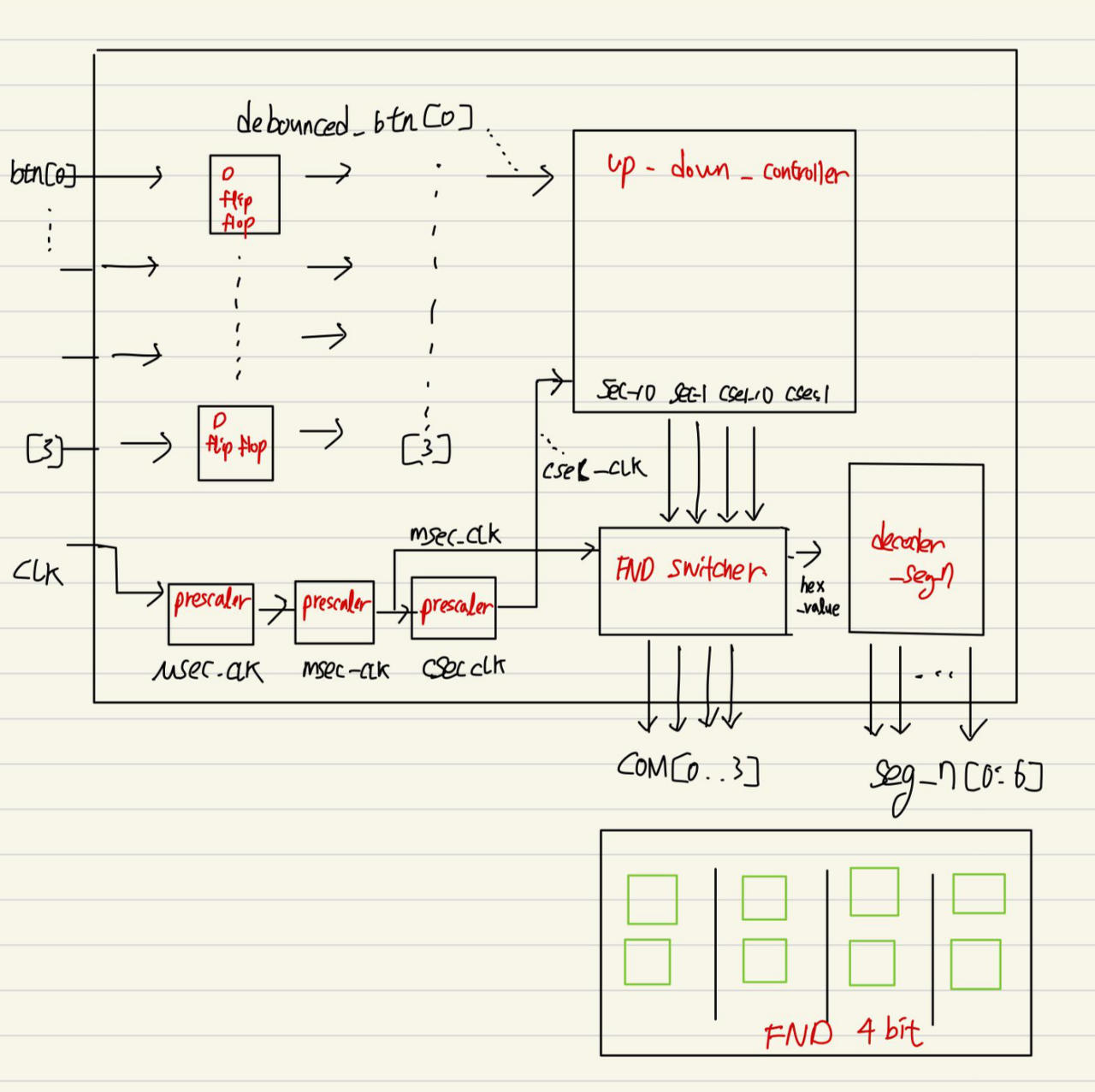

clk 신호에 맞춰 카운터 하는것을 생각해보자,

그렇다면 1초마다 생성되는 clock 신호에 맞춰 카운트가 된다고하면, 자연스럽게 1초간격으로 값이 올라가는 시계를 만들수 있다.

다음은 clk 신호에 맞춰 카운트 다운/업 하는 code이다.

module counter_up_down(

input up_down,

input up_down_clk,

input reset,

output reg [3:0] count_100 = 0,

output reg [3:0] count_1000 = 0,

output reg dec_clk = 0

);

always @(posedge up_down_clk or posedge reset) begin

if(reset) begin

count_100 <= 0;

count_1000 <= 0;

end

else begin

if(!up_down) begin

if(count_100 == 9) begin

count_100 <= 0;

if(count_1000 == 5) begin

count_1000 <= 0;

end

else begin

count_1000 <= count_1000 + 1;

end

end

else begin

count_100 <= count_100 + 1;

end

end

else begin

if(count_100 == 0) begin

count_100 <= 9;

if(count_1000 == 0)begin

count_1000 <= 5;

dec_clk <= 1;

end

else begin

count_1000 <= count_1000 - 1;

end

end

else begin

count_100 <= count_100 - 1;

dec_clk <= 0;

end

end

end

end

endmodule

module counter_up_down_csec(

input up_down,

input up_down_clk,

input reset,

output reg [3:0] count_1 = 0,

output reg [3:0] count_10 = 0,

output reg inc_clk = 0

);

always @(posedge up_down_clk or posedge reset) begin

if(reset) begin

count_1 <= 0;

count_10 <= 0;

end

else begin

if(!up_down) begin

if(count_1 == 9) begin

count_1 <= 0;

if(count_10 == 9) begin

count_10 <= 0;

inc_clk <= 1;

end

else begin

count_10 <= count_10 + 1;

end

end

else begin

count_1 <= count_1 + 1;

inc_clk <= 0;

end

end

else begin

if(count_1 == 0) begin

count_1 <= 9;

if(count_10 == 0)begin

count_10 <= 9;

end

else begin

count_10 <= count_10 - 1;

end

end

else begin

count_1 <= count_1 - 1;

end

end

end

end1. Prescaler

2021.04.01 - [반도체/FPGA - Verilog] - [FPGA] Clock에 필요한 모듈 1) Prescaler Verilog Code

2. FND Switcher

2021.04.01 - [분류 전체보기] - [FPGA] Clock에 필요한 모듈 2) FND 4digit switcher Verilog Code

3. Decoder 7_seg

2021.04.01 - [분류 전체보기] - [FPGA] Clock에 필요한 모듈 3) Decoder for 7 Segments Verilog Code