| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 |

- 임베디드시스템

- atomic access

- AMBA

- ABMA

- FPGA

- ordering model

- tff

- ERROR RESPONSE

- 구조적모델링

- AXI3

- stepmotor

- single copy atomic size

- out-of-order

- Multiple outstanding

- Verilog

- Low-power Interface

- QoS

- Multiple transaction

- T flip flop

- STM32

- SoC

- Interoperability

- 펌웨어

- 레지스터슬라이스

- 카운터

- FGPA #반도체설계 #verilog #시프트레지스터 #uart

- APB3

- AXI4

- cacheable

- 스텝모터

- Today

- Total

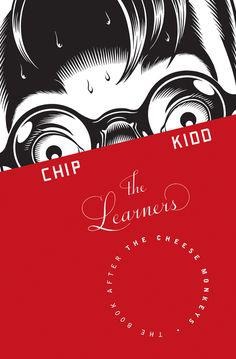

CHIP KIDD

[SDC] Synopsys Design Constraint 본문

그동안의 세미나, 독학 그리고 어깨넘어로 배운 것들 정리 차원

Design Sanity 에서 CDC, dc_lint, blk_sim 이라는 게 있다.

이런 것들을 하다보면 SDC, UPF, VCLP, UVM 등등의 용어를 들을 때가 있을것이다.

SDC 라는게 무엇이나? Synopsys Design Constraint 의 약자이며, 디자인 constraints 와 timing에 관한 정보를 기술한 문서이다. TCL 문법 규칙을 따른다.

SDC는 Synthesis, STA, Layout에 필수 이며,

DC(Design Compiler), PT(Prime Time)tool을 통해 사용이된다.

Constraints in SDC file

A. SDC VERSION:

ex> set sdc_version 2.1

B. Units:

time, resistance, capacitance , voltage, current, power 등의 다양한 단위가 set_units 라는 명령어로 명시된다.

ex> set_units -time ns -resistance Kohm -capacitance pF -voltage V -current mA

C. System Interface

1. Set driving cells

2. Set load

D. Design Rule Constraints

maximum fanout, maximum and minimum capacitance, maximum transition time

1. Set maximum fanout:

최대 fanout load이 특정한 input port로 set 됨.

Syntax : set_max_fanout fanout_value object_list

ex> set_max_fanout 5 [get_ports {port[10]}]

ex> set_max_fanout 10 [current_design] ← USI sdc

2. Set maximum transition

최대 전송 수는 아래의 명령을 통해 특정한 input port 디자인에 셋됨

Syntax : set_max_transition transition_value [-data_path] [-clock_path] object_list

ex> set_max_transition 2.5 [get_ports IN]

ex> set_max_transition 1 [current_design] ← USI sdc

3. Set maximum capacitance

ex> set_max_capacitance 0.5 [get_ports {GPP4_PAD_IN[0]}] ← PERIC_IO sdc

E. Timing Constraints ***

Clock definition, clock group, clock latency, clock uncertainty, clock transition, input delay, output delay, timing derates etc...

1. Create clock:

Syntax:

create_clock [clock_sources][-name clock_name] [-period value][-waveform edge_list][-add][-comment]

이 명령을 통해 현재 디자인(block)에서 clock object를 생성한다. 그리고 clock source로서 source objects를 명시하는 것이다.

ex> create_clock "u13/z" -name "CLK" -period 30 -waveform {12.0 27.0}

ex> create_clock [get_ports IPCLK] -name IPCLK -period 5.0 -waveform {0 2.5} ← USI sdc

2. Create generated clock:

Syntax : create_generated_clock [-name clock_name] [-add] source_objects -source master_pin [-master_clock clock] [-divide_by divide_factor | -multiply_by multiply_factor ] [-duty_cycle percent] [-invert] [-preinvert] [-edges edge_list] [-edge_shift edge_shift_list] [-combinational]

이 명령을 통해 generated clock object 를 생성한다. 핀또는 포트는 generated clock object에 명시되어야 한다.

generated clock은 master clock를 따른다. 그래서 master clock이 변할때마다 generated clock 또한 자동으로 변경된다.

generated clock은 분주된 clock으로 생성 될 수 있다.

ex> create_generated_clock -multiplied_by 3 -source CLK [get_pins div3/Q]

3. Group path:

그룹화는 function calculations를 위한 paths와 endpoints 의 세트이다. 그룹화를 사용하면 다른 그룹에 더 큰 위반이 있을 수 있는 경우에도 최적화(optimize)할 경로 그룹을 지정할 수 있게한다.

그리고 endpoint가 지정되면, 해당 끝 경로로 이어지는 모든 경로가 그룹화 된다.

Syntax: group_path [-weight weight_value] [-critical_range range_value] -default | -name group_name [-from from_list | -rise_from rise_from_list | -fall_from fall_from_list] [-through trough_list | -rise_through rise_through_list -fall_through fall_through_list] [-to to_list | -rise_to rise_to_list | -fall_to fall_to_list] [-comment comment_string] [-priority priority_level]

ex>

group_path -name "group1" -weight 2.0 -to {CLK1A CLK1B}

group_path -name GROUP1 -from [get_ports ABC/in3] -to [get-ports FF1/D]

4. Input delay:

5. Output delay:

delay 부분은 따로 설명

F. Timing Exception

1. Multicycle paths:

2. False paths

'반도체 > SoC' 카테고리의 다른 글

| [STA] Static Timing Analysis (0) | 2022.01.17 |

|---|---|

| ARM AMBA AXI4 protocol Spec 리뷰 [2/2] (0) | 2021.06.30 |

| ARM AMBA AXI4 protocol Spec 리뷰 [1/2] (0) | 2021.06.29 |

| ARM AMBA BUS 3 APB Spec 리뷰 (0) | 2021.06.03 |