| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- AXI4

- FGPA #반도체설계 #verilog #시프트레지스터 #uart

- Verilog

- 카운터

- ERROR RESPONSE

- tff

- STM32

- cacheable

- stepmotor

- APB3

- 레지스터슬라이스

- AXI3

- T flip flop

- ABMA

- AMBA

- 스텝모터

- Multiple outstanding

- 펌웨어

- QoS

- Interoperability

- 구조적모델링

- single copy atomic size

- out-of-order

- Multiple transaction

- 임베디드시스템

- ordering model

- FPGA

- SoC

- Low-power Interface

- atomic access

- Today

- Total

목록반도체/FPGA - Verilog (18)

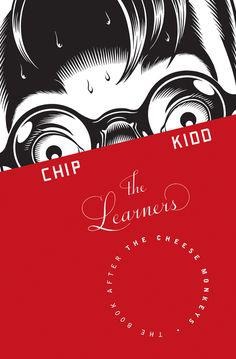

CHIP KIDD

[FPGA] I2C RTC module Design (verilog Code)

[FPGA] I2C RTC module Design (verilog Code)

이번시간에는 FPGA를 이용하여 I2C 통신 모듈이 탑재된 RTC 모듈을 설계해 보았습니다. DS3231 또는 DS1307은 I2C 통신 RTC 모듈로 잘 알려져 있습니다. 저는 DS1307을 기반으로 하여 제작했습니다. 따라서 블록다이어그램을 보면 다음과 같은데, 여기서 I2C , RTC 그리고 오실레이터 역할을 해주는 Prescaler를 설계했습니다. I2C 통신 특성 Datasheet를 보면 위의 순서로 데이터가 송수신이 되는데 , 위 State Machine을 설계해야합니다. Clock 특성은 SCL 이 High 일떄는 SDA의 값은 변하면 안됩니다. 하지만 예외가 있는데 Start 신호는 SCL이 High일떄 SDA가 LOW로 떨어지면 START 신호를 나타내며, SCL이 LOW일때 SDA가 H..

[FPGA-Verilog : encoder / decoder/ 디코더를 이용한 7seg 출력]

[FPGA-Verilog : encoder / decoder/ 디코더를 이용한 7seg 출력]

디코더 / 인코더 디코더 module decoder_3_8( input a, b, c, output [7:0] decode ); wire not_a, not_b, not_c; not (not_a, a); not (not_b, b); not (not_c, c); and (decode[0], not_a, not_b, not_c); and (decode[1], not_a, not_b, c); and (decode[2], not_a, b, not_c); and (decode[3], not_a,b, c); and (decode[4], a, not_b, not_c); and (decode[5], a, not_b, c); and (decode[6], a, b, not_c); and (decode[7], a, b, c..

[FPGA] Verilog Code - multiplexer/ demultiplexer

[FPGA] Verilog Code - multiplexer/ demultiplexer

1. Multiplexer module mutiplexer_8_1( input [7:0] D, input [2:0] S, output Y ); wire Sbar0, Sbar1, Sbar2; wire [7:0] w; not (Sbar0, S[0]); not (Sbar1, S[1]); not (Sbar2, S[2]); and (w[0], D[0], Sbar2, Sbar1, Sbar0); and (w[1], D[1], Sbar2, Sbar1, S[0]); and (w[2], D[2], Sbar2, S[1], Sbar0); and (w[3], D[3], Sbar2, S[1], S[0]); and (w[4], D[4], S[2], Sbar1, Sbar0); and (w[5], D[5], S[2], Sbar1, S..

[FPGA-Verilog : 2bit comparator (동작점 모델링)]

[FPGA-Verilog : 2bit comparator (동작점 모델링)]

동작점 모델링 if 내부의 조건을 만족하면 실행문 실행 --> 4bit, 8bit로 키워가도 똑같이 해주면되므로 동작점 모델링이 편하다. 반면에 Adder는 half adder를 붙여서 만들어가기 때문에 구조적 모델링 방법이 편리하다. module comparator_2bit( input [1:0] in1, input [1:0] in2, output reg less, output reg equal, output reg bigger ); always @(in1 or in2)begin if (in1 == in2)begin equal = 1; less = 0; bigger = 0; end if (in1 > in2)begin equal = 0; less = 0; bigger = 1; end if (in1 < i..

[FPGA] Verilog : 4bit Full adder (구조적 모델링, 데이터 flow 모델링)

[FPGA] Verilog : 4bit Full adder (구조적 모델링, 데이터 flow 모델링)

위아래 덧샘 후 led 전등 module fadder( input x, input y, input cin, output sum, inout cout ); wire s0, co0, co1; hadder ha0 (x,y, s0, co0); hadder ha1 (cin, s0, sum, co1); or u0 (cout, co0, co1); //assign sum = x^y^cin; //assign cout = (x&y)|(x&cin)|(y&cin); endmodule module fadder_4_bit(Cin, X, Y, Sum,Cout); output Cout; output [3:0]Sum; input Cin; input [3:0]X,Y; wire c0,c1,c2; fadder adder0(X[0], Y[0..

[FPGA] ADC ADC-Mux 설계 (Verilog Code) , 가변저항 10진수 출력

[FPGA] ADC ADC-Mux 설계 (Verilog Code) , 가변저항 10진수 출력

이번장은 ADC모듈을 이용하여 , 6번 채널을 통해서 가변저항의 값을 10진수로 출력하겠습니다. module channel6_ADC( input clk, input vauxp6, vauxn6, output [3:0] com, output [6:0] seg_7 ); wire clk_usec, clk_msec; wire [3:0] hex_value; wire [4:0] channel_out; wire eoc_out; wire [15:0]do_out; wire [3:0] ones, tens, hundreds, thousands; clock_usec G_usec (.clk(clk), .clk_usec(clk_usec)); clock_msec G_msec (.clk_usec(clk_usec), .clk_msec(..

[FPGA] ADC ADC-Mux 설계 (세팅)

[FPGA] ADC ADC-Mux 설계 (세팅)

ADC 는 아날로그 회로라 FPGA로는 설계가 불가능하다. 하지만 zybo 보드는 ADC하날로그 회로를 제공한다. 이번에는 ADC Mux 를 설계하겠다. ADC는 8개의 채널과 연결되어있다. 예를들어 각 채널마다 습도, 온도, 조도등으로 값을 읽어올 수 있도록 설계가 되어있다면 , ADC는 여기서 하나의 채널만 output으로 출력시킨다. 그럼 이런 기능을 해주는게 뭘까? 바로 Multiplexer이다. 즉 ADC MUX 는 8개의 채널중 하나의 채널을 output으로 뽑도록 해주는 모듈이다. 먼저 세팅하는 거부터..! 지보마스터에 들어가면 JA 단자에 ADC 포트가 따로 있다. 여기서 포트를 오픈 IP 소스를 누르면 vivado에서 제공하는 xadc IP가 있다. 들어가서 위 코드를 복사하여. ADD ..

카운트다운 모듈 동작 목표 1) 1번버튼을 누르면 초단위 UP 2) 2번버튼 누르면 min단위 UP 3) 3번버튼 누르면 Reset 초기화 4) 4번 버튼 누르면 Count Down 시작 + 카운트 다운중에 0이 되면 자동으로 동작 멈추고 0으로 고정되며 불이켜짐 Dflipflop : 버튼의 채터링 방지 Tflipflop : T가 1일때, Clk에 어떤 값을 입력하면, 버튼 처럼 Toggle 되는 Output을 낼때 + 리셋값이 들어오면 출력값을 안내도록 할때 아래 코드를 보면 T1까지 기본 타이머 구현이고, 그 이후는 0값이 되면 카운트 다운이 자동으로 멈춰 0으로 초기화 하고, LED가 켜짐을 나타내는 코드 module cook_timer_module( input clk, input [3:0] btn..