| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | |||||

| 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| 17 | 18 | 19 | 20 | 21 | 22 | 23 |

| 24 | 25 | 26 | 27 | 28 | 29 | 30 |

| 31 |

Tags

- atomic access

- 구조적모델링

- FGPA #반도체설계 #verilog #시프트레지스터 #uart

- 스텝모터

- Low-power Interface

- AMBA

- stepmotor

- ordering model

- STM32

- Interoperability

- tff

- ERROR RESPONSE

- APB3

- QoS

- Multiple transaction

- AXI4

- T flip flop

- Verilog

- 카운터

- 펌웨어

- cacheable

- 임베디드시스템

- out-of-order

- ABMA

- 레지스터슬라이스

- single copy atomic size

- FPGA

- AXI3

- SoC

- Multiple outstanding

Archives

- Today

- Total

목록Verilog (1)

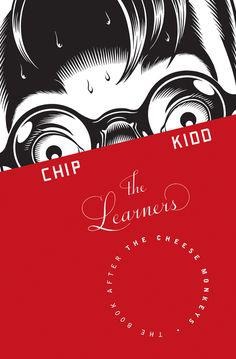

CHIP KIDD

[FPGA] T Flip Flop 을 이용한 up/down Counter 모듈 설계

[FPGA] T Flip Flop 을 이용한 up/down Counter 모듈 설계

용어정리 순차논리회로 : 플립플롭, 래치 --> 메모리를 이용하여 데이터 저장 가능 조합논리회로 : 논리 게이트, mux/demux, decoder/encoder 동기식 비동기식 회로 차이 : 동일 CLk을 이용한 회로 → 동기식, 각각의 다른 clk을 이용한 회로 →비동기식 카운터는 무수히 많은 곳에 사용된다. 시계뿐만 아니라, 수를 계산하고, 순서를 계산하고, 인터럽터, 번호표 등 매우 많은 곳에 사용된다. 따라서 이번시간에 카운터 모듈을 만들어 보고자 한다. 재활용이 가능한 카운터를 구조적 모델링을 통해 만들어 보고, 더나아가 뒤에있을 구조적 모델링을 통한 시계를 만들어보자. T Flip Flop : T에 신호가 들어올때 출력 toggle( 초기값 필요 → Q = 0) 시뮬레이션 결과를 보면 CLK..

반도체/FPGA - Verilog

2021. 3. 12. 15:47