| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 | 31 |

Tags

- FGPA #반도체설계 #verilog #시프트레지스터 #uart

- ABMA

- stepmotor

- tff

- 카운터

- QoS

- FPGA

- Multiple outstanding

- single copy atomic size

- Interoperability

- 구조적모델링

- SoC

- Verilog

- AXI4

- APB3

- ordering model

- Low-power Interface

- 펌웨어

- T flip flop

- AMBA

- Multiple transaction

- STM32

- atomic access

- AXI3

- ERROR RESPONSE

- cacheable

- out-of-order

- 임베디드시스템

- 레지스터슬라이스

- 스텝모터

Archives

- Today

- Total

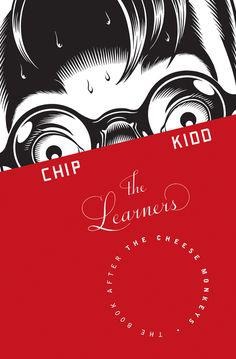

CHIP KIDD

FPGA/ ASIC/ SoC 구분 본문

itrustme.tistory.com/entry/FPGA%EC%99%80-ASIC%EC%9D%98-%EC%B0%A8%EC%9D%B4%EC%A0%90

FPGA와 ASIC의 차이점

FPGA와 ASIC의 차이점은 생각보다는 쉽습니다. FPGA와 ASIC의 설계방법은 비슷합니다.먼저 언급드린 것처럼 VHDL이나 회로를 ORCAD에서처럼 직접 그리는 것을 일컫는 스키메틱 캡쳐 방식등을 이용해서

itrustme.tistory.com

오래된 글이지만. 이해하기가 쉬워서 링크걸었습니다. 문제 시 삭제하겠습니다.

'반도체 > FPGA - Verilog' 카테고리의 다른 글

| [FPGA] - Stop Watch 구현하기 (Verilog C) (1) | 2021.03.31 |

|---|---|

| [FPGA] Manual (0) | 2021.03.12 |

| [FPGA] T Flip Flop 을 이용한 up/down Counter 모듈 설계 (0) | 2021.03.12 |

| [FPGA ] Verilog 분,초 시계 만들기 / 동작점 모델링 (0) | 2021.03.11 |

| [FPGA] 시프트 레지스터 Shift Register - SIPO/PISO (0) | 2021.03.11 |