| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- Interoperability

- stepmotor

- 레지스터슬라이스

- AXI4

- T flip flop

- single copy atomic size

- cacheable

- 카운터

- ERROR RESPONSE

- out-of-order

- 펌웨어

- APB3

- Low-power Interface

- SoC

- 임베디드시스템

- 스텝모터

- FPGA

- STM32

- Multiple transaction

- QoS

- AMBA

- AXI3

- tff

- atomic access

- FGPA #반도체설계 #verilog #시프트레지스터 #uart

- ABMA

- Verilog

- 구조적모델링

- ordering model

- Multiple outstanding

- Today

- Total

목록분류 전체보기 (48)

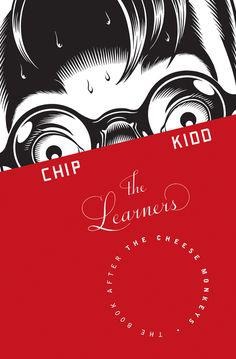

CHIP KIDD

카운트다운 모듈 동작 목표 1) 1번버튼을 누르면 초단위 UP 2) 2번버튼 누르면 min단위 UP 3) 3번버튼 누르면 Reset 초기화 4) 4번 버튼 누르면 Count Down 시작 + 카운트 다운중에 0이 되면 자동으로 동작 멈추고 0으로 고정되며 불이켜짐 Dflipflop : 버튼의 채터링 방지 Tflipflop : T가 1일때, Clk에 어떤 값을 입력하면, 버튼 처럼 Toggle 되는 Output을 낼때 + 리셋값이 들어오면 출력값을 안내도록 할때 아래 코드를 보면 T1까지 기본 타이머 구현이고, 그 이후는 0값이 되면 카운트 다운이 자동으로 멈춰 0으로 초기화 하고, LED가 켜짐을 나타내는 코드 module cook_timer_module( input clk, input [3:0] btn..

[FPGA] Clock에 필요한 모듈 4) Up/Down Counter Verilog Code

[FPGA] Clock에 필요한 모듈 4) Up/Down Counter Verilog Code

clk 신호에 맞춰 카운터 하는것을 생각해보자, 그렇다면 1초마다 생성되는 clock 신호에 맞춰 카운트가 된다고하면, 자연스럽게 1초간격으로 값이 올라가는 시계를 만들수 있다. 다음은 clk 신호에 맞춰 카운트 다운/업 하는 code이다. module counter_up_down( input up_down, input up_down_clk, input reset, output reg [3:0] count_100 = 0, output reg [3:0] count_1000 = 0, output reg dec_clk = 0 ); always @(posedge up_down_clk or posedge reset) begin if(reset) begin count_100

[FPGA] Clock에 필요한 모듈 3) Decoder for 7 Segments Verilog Code

[FPGA] Clock에 필요한 모듈 3) Decoder for 7 Segments Verilog Code

FND Switcher를 통해서 자리에 대한 Data가 나왔다면, FND에 나타낼 숫자에 대한 Date가 필요하다. Switcher에서 Hex_Value라는 숫자 Data가 생성이 되지만, 사실 UP_Down_counter에서 자리위치 뿐만아니라 숫자에 대한 정보가 Output으로 나온다. FND Swicher에서 4bit 의 COM과 Hex_Value가 나온다. 4자리 자리수를 나타내기에는 4bit는 충분하지만, 1부터 10까지 나타내는데 있어서 7bit의 이진숫자가 존재한다. 따라서 4bit로 도출된 Hex_Value 를 7bit의 2진수로 풀어야하는데 이런 기능을 하는게 Decoder 이다. 따라서 다음은 7segment를 위한 Decoder의 코드이다. module FND4digit_switche..

[FPGA] Clock에 필요한 모듈 2) FND 4digit switcher Verilog Code

[FPGA] Clock에 필요한 모듈 2) FND 4digit switcher Verilog Code

prescaler를 통해서 나눠진 단위 clock들에 맞춰 Up/Down Conuter모듈을 지나 생성된 초분시에 대한 Data는 4bit의 COM[0:3] 출력으로 나온다. 이 COM 출력은 4자리의 FND출력의 자리를 나타내는 Data이다. 따라서 이 자리수 데이터 값을 나타내는 FND Switcher 코드는 다음과 같다. module FND4digit_switcher( input [3:0] value_1, input [3:0] value_10, input [3:0] value_100, input [3:0] value_1000, input clk_msec, output reg [3:0] com, output reg [3:0] hex_value ); always @(negedge clk_msec) be..

[FPGA] Clock에 필요한 모듈 1) Prescaler Verilog Code

[FPGA] Clock에 필요한 모듈 1) Prescaler Verilog Code

Block Diagram 먼저, FPGA zybo 에서 제공하는 CLOCK (125Mhz) 을 usec, msec, sec 단위등으로 나눠, 단위별로 카운터하는데 필수가 되는 모듈입니다. 1. Prescaler (clk / usec_clk / msec_clk / csec_clk / sec_clk ) module clock_usec(input clk, output reg clk_usec); reg [6:0] cnt_clk; always @(negedge clk) begin cnt_clk = cnt_clk + 1; if (cnt_clk > 124) cnt_clk = 0; if (cnt_clk > 63) clk_usec = 1; else clk_usec = 0; end endmodule module clock..

[FPGA] - Stop Watch 구현하기 (Verilog C)

[FPGA] - Stop Watch 구현하기 (Verilog C)

Stop Watch 도 Timer와 마찬가지로 다음의 구조로 이루어져 있습니다. up_down_controller를 어떻게 설계하느냐에 따라 Timer가 될수도있고 Stop Watch가 될 수 있습니다. Stopwatch_module 회로를 다음과 같이 설계하였습니다. 버튼 1번 : Count Up 버튼 3번 : Reset 따라서 위 두개의 설계도를 기반으로 설계를 한 결과물 입니다. 아래는 StopWatch Module Verilog Code 부분입니다. module stop_watch_module( input clk, input [3:0] btn, output [3:0] com, output [6:0] seg_7 ); wire up_down = 0; wire [3:0] csec_1, csec_10, ..

[ARM] I2C 통신을 이용한 DS3231 RTC(Real Time Clock) 구현

[ARM] I2C 통신을 이용한 DS3231 RTC(Real Time Clock) 구현

I2C를 이용해서 DS3231으로 부터 시간값을 얻자, 얻은 값을 OLED에 송출하기 (이건 SPI) /* * ds3231.c * * Created on: Mar 22, 2021 * Author: kccistc */ #include "ds3231.h" I2C_HandleTypeDef *hi2c; void DS3231_Init(I2C_HandleTypeDef *I2C_Handler) { hi2c = I2C_Handler; } void I2C_Transmit(uint8_t devAddr, uint8_t memAddr, uint8_t *pData, uint16_t Size ) { HAL_I2C_Mem_Write(hi2c, (devAddr day = BCDtoDEC(getDate[0]); sDate -> dat..

[ARM] 엘레베이터 프로젝트 - SPI 통신을 이용한 OLED 구현

[ARM] 엘레베이터 프로젝트 - SPI 통신을 이용한 OLED 구현

UART I2C SPI 1:1 1:N 1:N 비동기 동기 동기 slave device 주소 chip select (pin 개수 증가 단점) slow fast 통신 단순 복잡 단순 ※ 동기 vs 비동기 기준신호 : Clock Clock을 생성하는 것 : Master / Clock을 받는 것 : Slave → Clock을 기준으로 동작 하는 것 : 동기 SPI 동작 구조 ※ MOSI : Master Out Slave In → Write MISO : Master In Slave Out → Read 특징 Bit 단위 신호로 데이터 전송 SCLK (동기신호)에 맞춰 Write 하고 Read 함 CPOL (0) : 시작위치 HIGH (1) : 시작위치 LOW CPHA (0) : 첫번째 Edge에서 동기화 (1) :..